Контроллер lpc что это

Контроллер lpc что это

Используемая вами версия браузера не рекомендована для просмотра этого сайта.

Установите последнюю версию браузера, перейдя по одной из следующих ссылок.

Спецификация интерфейса LPC для устаревших систем ввода/вывода способствовала переходу отрасли на системы без шины ISA. Ключевым усовершенствованием версии 1.1 спецификации интерфейса LPC является включение циклов встроенного ПО и добавление возможности многобайтового чтения.

Интерфейс LPC позволяет устаревшим компонентам ввода-вывода на системной плате, обычно встроенным в микросхему Super I/O, перейти с шины ISA/X на интерфейс LPC, сохраняя полную программную совместимость. Спецификация LPC предлагает несколько ключевых преимуществ по сравнению с шиной ISA/X, например сокращение числа выводов для получения более простой и экономичной конструкции. Спецификация интерфейса LPC понятна для функций ввода/вывода и совместима с существующими периферийными устройствами и приложениями.

Спецификация интерфейса LPC описывает операции памяти, системы ввода/вывода и прямого доступа к памяти (DMA). В отличие от шины ISA, которая работает с частотой 8 МГц, она использует тактовую частоту PCI 33 МГц и совместима с более продвинутыми кремниевыми процессорами. Дизайнеры мобильных устройств также оценят преимущества уменьшения числа выводов, поскольку шина занимает меньше места, потребляет меньше энергии и более эффективна с точки зрения температурных характеристик. Спецификацию интерфейса LPC версии 1.1 и соответствующее обоюдное лицензионное соглашение о патентах можно скачать ниже.

Контроллер lpc что это

LPC (Low Pin Count, малое число контактов) — шина, разработанная компанией Intel и предназначенная главным образом для подключения стандартных устройств, доставшихся современным персональным компьютерам «в наследство» от ранних ПК и обычно называемых унаследованными (legacy). Раньше такие устройства подключались к шине ISA.

Целесообразность разработки новой шины объясняется следующими основными причинами:

Шина LPC имеет всего 7 обязательных и 6 необязательных сигналов. Обмен данными по ней идёт в синхронном режиме с частотой 33 МГц (шина ISA является асинхронной, что также усложняет работающее с ней оборудование), причём каждый так передаётся 4 информационных или управляющих бита. Разрядность адреса увеличена до 32 бит, что позволяет задатчикам шины прямо обращаться к адресному пространству памяти объёмом 4 Гбайта (у шины ISA разрядность адреса составляла 24 бита, что ограничивало возможности адресации величиной 16 Мбайт). Реальная пропускная способность LPC, составляющая 6,7 Мбайт/с, ненамного уступает таковой у ISA (до 8 Мбайт/с) и совершенно достаточна для одновременной работы всех подключенных к ней устройств (по расчётам Intel, они используют порядка 75% максимальной пропускной способности).

С точки зрения программиста шина LPC как бы отсутствует: программы просто работают с регистрами подключенных к ней устройств. Хотя у LPC отсутствуют традиционные сигналы запросов прерываний и прямого доступа к памяти, эти возможности поддерживаются, причём создаётся иллюзия применения обычной шины ISA. Например, с точки зрения программиста подключенные к LPC порты и контроллер интерфейса PS/2 генерируют обычные для них запросы прерываний IRQ1, IRQ3, IRQ4, IRQ12, хотя физически эти линии отсутствуют. Определять наличие или отсутствие тех или иных устройств, подключенных к LPC, необходимо соответствующими функциями BIOS. Зачастую информация о них содержится в таблицах ACPI, поэтому анализ конфигурации обычно целесообразно начинать именно с их разбора.

Встроенный контроллер одного ноутбука и его наследство

В этом материале я хочу немного рассказать о том, что происходит во встроенном контроллере (Embedded Controller, EC) моего ноутбука. Речь идёт о мультиконтроллере IT8586E, основанном на Intel 8051. Он встроен в ноутбук Lenovo Ideapad 310-15IKB. Но, прежде чем переходить к деталям, полагаю, нелишним будет поговорить о том, что это вообще такое — встроенные контроллеры.

Краткая история встроенных контроллеров на платформах x86

Сначала был создан компьютер IBM PC. Многих это возмутило, данный шаг компании IBM был широко признан неразумным.

В материнскую плату этого компьютера было встроено множество периферийных устройств, вроде Intel 8259 (программируемый контроллер прерываний) или Intel 8253 (программируемый таймер). Обращаться к этим контроллерам можно было, пользуясь инструкциями in/out ядра x86 (и, на самом деле, к контроллерам 8259 и 8253 всё ещё можно обращаться на современных x86-процессоров, но теперь они входят в состав кристалла CPU). Один из контроллеров IBM PC, Intel 8255 (программируемый контроллер интерфейса периферийных устройств), отвечал за взаимодействие с клавиатурой.

Где-то в конце 1980-х периферийные устройства всё чаще и чаще объединяли, включая в состав одной микросхемы несколько таких устройств. Например — это чипы северного моста и южного моста. Один из таких чипов, Super I/O-контроллер, отвечал за взаимодействие с низкоскоростными устройствами, вроде последовательных портов, параллельных портов и контроллеров дисководов гибких дисков. В состав этого чипа часто входил и контроллер клавиатуры.

Ноутбукам, кроме прочего, требовалась особая система управления питанием. Производители портативных компьютеров взглянули на контроллер клавиатуры, на то, что он способен перезагружать компьютер, и сказали: «На самом деле — это замечательно. Давайте сделаем то, что нам нужно, по похожей схеме». В результате к контроллеру клавиатуры были добавлены два порта с похожим интерфейсом, позволяющим отправлять на устройства команды и получать от них данные. И, фактически, во многих платформах эта возможность реализована в том же самом контроллере, который входит в состав Super I/O-чипа.

В середине 1990-х заметным явлением стал стандарт ACPI (Advanced Configuration and Power Interface, усовершенствованный интерфейс управления конфигурацией и питанием). Он определял стандартизированный интерфейс для EC. А именно, через его командный интерфейс можно было обращаться к 8-битному адресному пространству переменных, определяемых производителями оборудования. Эти переменные можно было описывать с помощью языка AML (ACPI Machine Language), средствами AML можно было описывать и код, позволяющий воздействовать на эти переменные.

В конце 2000-х годов микросхемы южного и северного мостов были объединены с CPU. Правда, надо отметить, что интеграция южного моста (PCH, Platform Controller Hub) в CPU, по всей видимости, имеет место лишь на мобильных платформах. Но в ноутбуках EC всё ещё представлен отдельным чипом, который, кроме того, реализует функционал Super I/O-контроллера и контроллера клавиатуры. Он, например, решает следующие задачи:

Схема материнской платы моего ноутбука

Так как EC интенсивно взаимодействует с разными устройствами — неплохо было бы знать о том, что это за устройства. Мне в решении этой задачи повезло — кто-то выложил в интернет так называемые boardview-файлы к интересующей меня плате. В таких файлах содержатся схемы печатных плат, в частности, сведения о компонентах, расположенных на плате, и о том, как они связаны. Между компонентами материнских плат имеется так много соединений, что анализ схемы их связей может оказаться весьма сложной задачей. Я попытался представить связи между компонентами платы в упрощённой форме, результат моих трудов показан на следующей схеме (тут нет большинства линий, имеющих отношение к питанию).

Схема связей компонентов платы (оригинал)

CPU соединён с EC с использованием шины LPC (Low Pin Count), которая, по сути, представляет собой замену шины ISA, применявшейся в более старых компьютерах, в физической реализации которой используется меньше линий связи. Процессор и контроллер взаимодействуют, в основном, по LPC. Но между EC и CPU имеется множество соединений (показанных синими линиями без стрелок), используемых в особых целях. Например — это линия SCI, предназначенная для вызова прерывания от EC в CPU.

Прошивка EC

Раздобыть прошивку контроллера несложно. Я уже извлекал образ BIOS раньше, для других нужд. После его обработки с помощью утилиты cpu_rec в моём распоряжении оказалось примерно 160 Кб 8051-кода из самого начала образа, расположенного до кода, имеющего отношения к UEFI. Контроллер 8051 имеет 16-битное адресное пространство, а значит 160 Кб кода ему не соответствуют. Получается, что речь идёт о так называемой banked-прошивке. То есть — одни части («блоки» или «банки») прошивки в адресном пространстве подвергаются динамической замене на другие части путём воздействия на некие регистры.

Размеры блоков прошивки обычно, в большинстве контроллеров 8051, составляют либо 32, либо 64 Кб. Выяснить их размер при работе с конкретным контроллером можно, поискав повторяющиеся фрагменты кода. Дело в том, что в разных блоках прошивки обычно имеются одинаковые фрагменты, представляющие код общего назначения (быстро найти такие фрагменты можно попробовать, прибегнув к автокорреляции). Оказалось, что в моём случае речь идёт о блоках кода размером 32 Кб.

После того, как я всё это выяснил, меня посетила блестящая идея, которая заключалась в том, чтобы посмотреть даташит исследуемого компонента. Даташит на мой контроллер найти не удалось, но мне попались документы на IT8502E, описывающие устройство достаточно близкое к тому, которое было у меня. В нём, что было очень кстати, подробно описывалось большинство I/O-механизмов и, похоже, описание функционирования прошивки, в основном, соответствовало той прошивке, что была у меня.

При просмотре даташита я наткнулся на упоминание отладочного интерфейса I2C, но он, правда, не был документирован. После некоторых изысканий я нашёл проект ECSpy, который представляет собой Rust-реализацию отладчика для EC, созданную силами компании System76, которая работает над собственной прошивкой для EC.

Отладчик даёт доступ на чтение и запись к оперативной памяти и регистрам ввода/вывода EC. Доступ к регистрам отличается дополнительным ограничением, которое заключается в том, что операция записи чётко определена лишь для триггерных регистров (в результате, например, операция, вызывающая изменение состояния конечного автомата, не сработает).

Ещё в даташите сказано, что возможность отладки нужно включать с помощью регистра, но она и так включена. Доступ к ней осуществляется посредством I/O-портов x86 через Super I/O-чип, поэтому ей можно пользоваться из пользовательского пространства, без необходимости писать драйвер.

Для реверс-инжиниринга тех частей прошивки, которые отвечают за взаимодействие с различными устройствами, могут пригодиться спецификации этих устройств. Я, работая над этим проектом, прочитал часть спецификаций ACPI, SMBus и Smart Battery. В процессе исследования кода прошивки используются следующие ресурсы и инструменты: boardview-файлы, даташиты, спецификации компонентов, отладчик Ghidra, обычный браузер, применяемый для поиска дополнительных сведений вроде скан-кодов, исходный код Linux-драйвера для EC, дизассемблированный машинный ACPI-код, отладчик для EC и его исходный код. В таких делах весьма кстати могут оказаться несколько мониторов, использование которых позволяет ускорить сопоставление информации, полученной из разных источников.

Большой объём работы выполняется в коде главного цикла, ответственном за обработку событий таймера. Таймер в EC запрограммирован так, что он выдаёт прерывание раз в одну миллисекунду. Потом, на основе прерываний таймера, формируются события, которые происходят, например, каждые 10, 50, 100 мс. Обновление ACPI-переменных выполняется, в основном, в этом контексте.

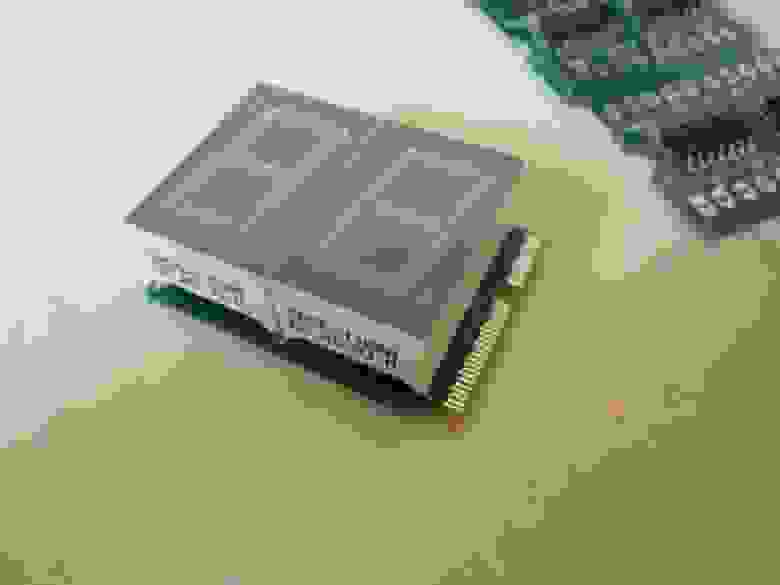

POST-карты в современных ноутбуках

Затем, вместе с тактовыми импульсами, осуществляется последовательный вывод результирующего значения на GPIO-пины.

Вышеприведённая поисковая таблица может показаться вам знакомой. Дело в том, что она позволяет преобразовывать полубайты в шестнадцатеричные числа для их вывода на 7-сегментном дисплее. Если взглянуть на схему материнской платы, там можно увидеть две линии — EC_TX и EC_RX (эти названия, вероятно, не очень удачны, так как одна из них — это линия данных, а другая — тактовая линия, обе они используются лишь для отправки данных). Они ведут к Wi-Fi-чипу, который подключён к плате через разъём M.2. Но эти линии, на самом деле, ни к чему на Wi-Fi-карте не присоединены.

Это наводит на мысль о том, что существуют некие POST-платы, которые можно подключать к разъёму M.2 для решения проблем, возникающих в ходе загрузки ноутбуков. Так как я знаком с протоколом обмена данными, используемым в M.2-картах, я попытался сделать собственный вариант такой платы (она, в целом, представляет собой два последовательно соединённых сдвиговых регистра, подключённых к 7-сегментным дисплеям). Посмотрите — какая симпатичная у меня получилась штука.

Самодельная POST-плата для разъёма M.2

Но я, к сожалению, видимо что-то напутал, так как эта плата, в итоге, так и не заработала, а мне не очень-то хотелось тратить время на поиск и исправление ошибок, допущенных при её создании.

Клавиатурные механизмы

Можно подумать, что вышеописанная задача решается очень легко, что заключается она в просмотре некоей поисковой таблицы и в отправке хосту результатов. Но, увы, скан-коды PS/2 — это настоящий бардак.

Существует три различных набора скан-кодов, между которыми нет ничего общего. EC использует набор №2. Одиночное нажатие и отпускание клавиши не всегда приводит к генерированию одного байта скан-кода.

Если промежуточное значение меньше 0x80, это значит, что оно просто соответствует обычному однобайтовому PS/2 скан-коду. А если говорить о других значениях, то они, по уже рассмотренной нами схеме, используются в роли индексов в поисковой таблице. Результирующее значение определяет функцию, которая используется для обработки скан-кода. Полученные скан-коды затем помещают в 16-байтовый кольцевой буфер, байты, содержащиеся в котором, если это возможно, потом отправляют хосту.

Таинственный фрагмент кода

Зачем встроенному контроллеру SHA-1? Если посмотреть на то, что именно вызывает SHA1-код, то окажется, что он используется при взаимодействии с батареей по SMBus:

Где хранится код?

Во многих прошивках для 8051 обычно имеется код, реализующий возможности отладки, и мой — не исключение. Перед функциями, имеющими отношение к контроллеру клавиатуры и к EC, имеется множество функций, которые явно реализуют отладочные возможности. Одна из них — это команда контроллера клавиатуры, предназначенная для чтения из EC данных с адресов флеш-памяти с применением регистра.

Если сделать оттуда дамп прошивки, то получится образ, который отличается от оригинала. Изначально я предполагал, что EC использует образ из флеш-памяти BIOS, так как он хранится в этой памяти, и EC к этой памяти подключён. Но оказалось, что это, на самом деле, не так. К этой памяти напрямую подключены и CPU, и EC. В результате, в том случае, если и тот и другой одновременно попытаются прочесть из неё данные, на шине неизбежно возникнет конфликт. Прошивка, на самом деле, хранится в самом EC. В IT8502 этой возможности не было (это запутало меня ещё сильнее, так как я пользовался даташитом именно для такого контроллера).

Запуск моего собственного кода в EC

Вероятно, стоит сказать о том, что у 8051 имеется некоторое количество различных адресных пространств:

Я этого делать не собирался, так как подобные действия несут в себе риск «окирпичивания» устройства. EC можно перепрограммировать, используя входы/выходы клавиатурной матрицы в роли параллельного порта, но я не собирался заниматься и этим.

Ещё одна проблема, связанная с записью данных во флеш-память, заключается в том, что её содержимое проверяется с использованием контрольной суммы. В прошивке имеется сигнатура, которая указывает на то, где начинается контрольная сумма, и в ней имеются два байта, которые различаются в разных редакциях прошивки. Подобное характерно для контрольных сумм. Если дело обстоит именно так — то неясно, где именно начинается и заканчивается контрольная сумма, и то, как именно она вычисляется.

Правда, для выполнения собственного кода нет нужды выполнять запись данных во флеш-память. В EC для этого имеется другой механизм. А именно — адреса 0x0000-0x1000 в адресном пространстве XDATA — это обычная оперативная память, которую можно отобразить на произвольную область адресного пространства CODE, изменив содержимое кое-каких регистров.

Схема из даташита, на которой показано 5 областей, пронумерованных от 0 до 4, которые могут быть отображены на адресное пространство кода. А именно, речь идёт об областях 0x0000-0x0800, 0x0800-0x0c00, 0x0c00-0x0e00, 0x0e00-0x0f00 и 0x0f00-0x1000

В результате для выполнения собственного кода достаточно лишь выполнить отображение одного из этих фрагментов на память с кодом. Оперативная память в диапазоне 0x0000-0x0e00 используется самой прошивкой, в результате остаются блоки 3 и 4, размер каждого из которых составляет 256 байт.

Правда, чтобы осуществить отображение этой памяти на память с кодом, нужно выполнить запись в регистры и в оперативную память из пространства XDATA. Есть одна отладочная функция, позволяющая писать данные в XDATA, но она содержит ошибки и может писать данные только по адресам, где байт из верхней части адреса является таким же, как и байт из его нижней части. Тут имеется ещё и интерфейс I2C, который достаточно хорошо подходит для решения задачи записи данных в SRAM.

Я сомневался по поводу записи данных в порты ввода/вывода, так как было сказано, что это подходит лишь для триггерных регистров. Но в регистрах, используемых для отображения памяти, имеется ещё и бит для запуска DMA-транзакции (так как этот чип, конечно, поддерживает DMA). В любом случае, не было способа проверить то, что отображение памяти осуществляется именно так, как мне нужно, так как нет отладочной функции, позволяющей читать данные из адресного пространства CODE.

К счастью, был и другой путь: функционал отображения памяти используется для перезаписи флеш-памяти (так как никто не заинтересован в том, чтобы работа программы завершилась бы с ошибкой, когда будет достигнута область с кодом, выполняющим запись данных). Используя I2C можно отредактировать содержимое SRAM в адресном пространстве XDATA, поместив туда отладочный код, и подстроить механизм записи данных во флеш-память так, чтобы он обращался бы к этому отладочному коду.

В любом случае, эту проблему легко обойти, так как между адресами, всё равно, имеется взаимно однозначное соответствие, а значит — код можно просто записать в те места пространства XDATA, которые будут соответствовать нужным местам памяти. Оказалось, что I2C-запись в регистры, отвечающие за отображение памяти, тоже работает. В результате для выполнения отладочного кода с его последующей записью мне не нужно было бы прибегать к режиму перезаписи флеш-памяти.

Итоги

На сегодня это всё, а в следующий раз я расскажу об исследовании прошивки ноутбучного Wi-Fi-модуля (RTL8821AE) и о разработке небольшого кейлоггера, основанного исключительно на возможностях Intel 8051.

Занимались ли вы разработкой прошивок для контроллеров, основанных на Intel 8051?

Прочитайте онлайн Аппаратные интерфейсы ПК. Энциклопедия | 6.4. Интерфейс LPC

Интерфейс LPC (Low Pin Count — малое число выводов) предназначен для локального подключения устройств, ранее использовавших шину X-Bus или ISA: контроллеров НГМД, последовательных и параллельных портов, клавиатуры, аудиокодека, BIOS и т.п. Введение нового интерфейса обусловлено изживанием шины ISA с ее большим числом сигналов и неудобной асинхронностью. Интерфейс обеспечивает те же циклы обращения, что и ISA: чтение-запись памяти и ввода-вывода, DMA и прямое управление шиной (bus mastering). Устройства могут вырабатывать запросы прерываний. В отличие от ISA/X-Bus с их 24-битной шиной адреса, обеспечивающей адресацию лишь в пределах первых 16 Мбайт памяти, интерфейс LPC имеет 32-битную адресацию памяти, что обеспечивает доступ к 4 Гбайт памяти. 16-битная адресация портов обеспечивает доступ ко всему пространству 64 К портов. Интерфейс синхронизирован с шиной PCI, но устройства могут вводить произвольное число тактов ожидания. Интерфейс программно прозрачен — как и для ISA/X-Bus, не требует каких-либо драйверов. Контроллер интерфейса LPC является устройством-мостом PCI. По пропускной способности интерфейс практически эквивалентен этим шинам. В спецификации LPC 1.0 приводится расчет пропускной способности интерфейса и устройств, его использующих. При наличии буферов FIFO интерфейс наиболее выгодно использовать в режиме DMA. В этом случае главным потребителем будет LPT-порт — при скорости передачи данных 2 Мбайт/с он займет 47% полосы интерфейса. Следующим будет инфракрасный порт — 4 Мбит/с (11,4%). Остальным устройствам (контроллер НГМД, СОМ-порт, аудиокодек) требуются еще меньшие доли, в результате они занимают до 75% полосы при одновременной работе. Таким образом, перевод этих устройств с ISA/X-Bus на LPC не должен вызывать проблем производительности более острых, чем были на старых шинах.

Интерфейс имеет всего 7 обязательных сигналов:

♦ LAD[3:0] — двунаправленная мультиплексированная шина данных;

♦ LFRAME# — индикатор начала и конца цикла, управляемый хостом;

♦ LRESET# — сигнал сброса, тот же, что и RST# на шине PCI;

♦ LCLK — синхронизация (33 Мгц), тот же сигнал, что и CLK на шине PCI;

Дополнительные сигналы интерфейса LPC:

♦ LDRQ# — кодированный запрос DMA/Bus Master от периферии;

♦ SERIRQ — линия запросов прерывания (в последовательном коде), используется, если нет стандартных линий запросов IRQ в стиле ISA;

♦ CLKRUN# — сигнал, используемый для указания на остановку шины (в мобильных системах), требуется только для устройств, нуждающихся в DMA/BusMaster в системах, способных останавливать шину PCI;

♦ РМЕ# — событие системы управления потреблением (Power Management Event), может вводиться периферией, как и в PCI;

♦ LPCPD# — Power Down, указание от хоста устройствам на подготовку к выключению питания;

♦ LSMI# — запрос прерывания SMI# для повтора инструкции ввода-вывода.

Рис. 6.15. Протокол LPC

В поле START возможны следующие коды:

♦ 0000 — начало цикла обращения хоста к устройству;

♦ 0010 — предоставление доступа ведущему устройству 0;

♦ 0011 — предоставление доступа ведущему устройству 1;

♦ 1111 — принудительное завершение цикла (abort).

Остальные коды зарезервированы.

Поле CYCTYPE задает тип и направление передачи. Бит 0 задает направление (0 — чтение, 1 — запись), биты [2:1] — тип обращения (00 — порт, 01 — память, 10 — DMA, 11 — резерв), бит 3 — резерв (0).

Поле ADDR служит для передачи адреса. В цикле памяти оно занимает 8 тактов (32 бита), в цикле ввода-вывода — 4 такта. Передача адреса начинается со старших битов (чтобы раньше срабатывал дешифратор адреса).

В поле DATA передаются данные. На каждый байт требуется 2 такта, передача начинается с младшей тетрады. Многобайтные передачи начинаются с младшего байта.

Поле SYNC служит для введения тактов ожидания устройством, к которому выполняется обращение. Оно может содержать следующие коды (остальные зарезервированы):

♦ 0000 — готовность (без ошибок), для DMA означает снятие запроса для данного канала;

♦ 0101 — короткое ожидание (несколько тактов);

♦ 0110 — длинное ожидание;

♦ 1001 — готовность и присутствие запроса для канала DMA (для других типов обращения недопустимо);

♦ 1010 — ошибка: данные переданы, но возникли условия, при которых на шинах PCI или ISA выработался бы сигнал SERR# или IOCHK# (для DMA также означает снятие сигнала запроса).

Поле синхронизации обеспечивает контроль передачи, введение тактов ожидания и механизм тайм-аутов. Начав цикл, хост читает поле синхронизации. Если в течение трех тактов адресованное устройство не ответит, хост считает, что его нет на шине, и прекращает транзакцию. Если приходит код короткого ожидания, хост дожидается его смены на готовность или ошибку, но после 8 тактов ожидания он прервет транзакцию по тайм-ауту. Код длинного ожидания может приходить сколь угодно долго, ответственность за отсутствие зависания ложится на адресованное устройство. При прямом управлении поле SYNC выставляется хостом, и устройство должно терпеливо ожидать готовности, без каких-либо тайм-аутов. В самом быстром варианте (без тактов ожидания) поле SYNC занимает один такт.

На рис. 6.16 приведена последовательность полей при обращениях хоста к памяти или портам (серым цветом помечены поля, вводимые устройством). Во всех этих обращениях передается по одному байту. Для чтения памяти, предполагая 5 тактов поля SYNC (время доступа к EPROM 120 нс), требуется 21 такт (0,63 мкс), что обеспечивает скорость чтения памяти 1,59 Мбайт/с. Если память конвейеризирована, то последующие обращения будут быстрее. Для записи в память поле SYNC займет 1 такт, а весь цикл — 17 тактов (0,51 мкс), что дает скорость записи 1,96 Мбайт/с. Обращения к портам за счет более короткой адресации и без тактов ожидания (1 такт SYNC) занимают по 13 тактов (0,39 мкс), что дает скорость 2,56 Мбайт/с для чтения и записи.

Рис. 6.16. Обращения к памяти и портам: а — чтение, б — запись

Рис. 6.17. Посылка запроса DMA или прямого управления

Передача данных DMA (рис. 6.18) выполняется под управлением хоста, но несколько отличается от обычных обращений к портам и памяти. Здесь появляются новые поля:

♦ поле SIZE определяет размер передачи: 0000 — 1 байт, 0001 — 2 байта, 0011 — 4 байта, остальные значения зарезервированы;

♦ поле CHANNEL служит для передачи хостом номера канала DMA (биты [2;0]) и признака конца цикла (TC, бит 3).

Рис. 6.18. Обращения DMA: а — чтение памяти, б — запись в память

Циклы чтения памяти, в зависимости от длины обращения (1, 2 или 4 байта), без тактов ожидания (они скрыты контроллером DMA) занимают 11, 18 и 32 тактов (0,33, 0,54 или 0,96 мкс), что обеспечивает производительность 3,03, 3,70 или 4,17 Мбайт/с соответственно. Циклы записи занимают 11,14 или 20 тактов (0,33, 0,42 или 0,60 мкс), что обеспечивает производительность 3,03, 4,76 или 6,67 Мбайт/с. На рисунке выделены рамкой последовательности полей, повторяющиеся при передаче 2 и 4 байтов.

Рис. 6.19. Обращения периферийного устройства (Bus Master): а — чтение памяти или порта, б — запись в память (порт)

Конфигурирование устройств LPC не предусматривает использования протоколов PCI или ISA PnP, поскольку все устройства LPC априорно известны системной BIOS. Для обращения к устройствам LPC хост должен декодировать их адреса и направлять обращения по ним на контроллер LPC.